新書推薦:

《

自由,不是放纵

》

售價:NT$

250.0

《

甲骨文丛书·消逝的光明:欧洲国际史,1919—1933年(套装全2册)

》

售價:NT$

1265.0

《

剑桥日本戏剧史(剑桥世界戏剧史译丛)

》

售價:NT$

918.0

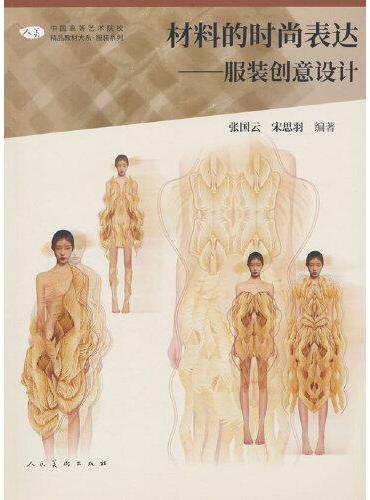

《

中国高等艺术院校精品教材大系:材料的时尚表达??服装创意设计

》

售價:NT$

347.0

《

美丽与哀愁:第一次世界大战个人史

》

售價:NT$

653.0

《

国家豁免法的域外借鉴与实践建议

》

售價:NT$

857.0

《

大单元教学设计20讲

》

售價:NT$

347.0

《

儿童自我关怀练习册:做自己最好的朋友

》

售價:NT$

316.0

|

| 編輯推薦: |

温德通老师这本《集成电路制造工艺与工程应用》,从几年前开始编写时就与我进行了沟通,在看过初稿后,我对于他亲自绘制的数百幅工艺流程图印象深刻,并且深感佩服,这些图片在目前讲述集成电路工艺的教材中是看不到的,这也是我决定这本书一定要采用彩色印刷的原因。而且教材往往囿于知识体系的完整,不可能将具体的工艺流程如此详细地讲解,而我们在学习的时候,对于教材中所叙述的工艺流程总是限制在名词术语之间,而温老师得益于他十多年在企业中的工作经验,弥补了这些不足,为读者奉上了这本佳作。

作为同是微电子学专业的我,深知这样的书在编写上的难度,以及找寻愿意去写这样的书的作者有多难。本书的出现,相信一定会为集成电路领域做出很大的贡献!这个领域虽然小众,但是对于和传统教科书有所区别,具有鲜明特点和针对性的图书的需求,我一直相信是有的,而且很大。

在编写时,温老师数易其稿,并且力求简明和清晰,这不是一本大而全的教科书,但却是工艺方面难能可贵的参考资料,希望能收到各位半导体集成电路从业者的喜爱。正如温老师在扉页中所写的那句话一样:谨以此书,献给所有热爱半导体行业的朋友!

|

| 內容簡介: |

本书以实际应用为出发点,对集成电路制造的主流工艺技术进行了逐一介绍,例如应变硅技术、HKMG技术、SOI技术和FinFET技术,然后从工艺整合的角度,通过图文对照的形式对典型工艺进行介绍,例如隔离技术的发展、硬掩膜版工艺技术、LDD工艺技术、Salicide工艺技术、ESD IMP工艺技术、AL和Cu金属互连。然后把这些工艺技术应用于实际工艺流程中,通过实例让读者能快速的掌握具体工艺技术的实际应用。

本书旨在向从事半导体行业的朋友介绍半导体工艺技术,给业内人士提供简单易懂并且与实际应用相结合的参考书。本书也可供微电子学与集成电路专业的学生和教师阅读参考。

|

| 關於作者: |

|

温德通,IC高级设计工程师。毕业于西安电子科技大学微电子学院,曾供职于中芯国际集成电路制造(上海)有限公司,负责工艺制程整合方面的工作;后加入晶门科技(深圳)有限公司工作至今,负责集成电路工艺制程、器件、闩锁效应和ESD电路设计等方面的工作。

|

| 目錄:

|

专家推荐

写作缘由与编写过程

致谢

第1章 引言

1.1崛起的CMOS工艺制程技术

1.1.1 双极型工艺制程技术简介

1.1.2 PMOS工艺制程技术简介

1.1.3 NMOS工艺制程技术简介

1.1.4 CMOS工艺制程技术简介

1.2 特殊工艺制程技术

1.2.1 BiCMOS工艺制程技术简介

1.2.2 BCD工艺制程技术简介

1.2.3 HV- CMOS工艺制程技术简介

1.3 MOS集成电路的发展历史

1.4 MOS器件的发展和面临的挑战

参考文献

第2章 先进工艺制程技术

2.1 应变硅工艺技术

2.1.1 应变硅技术的概况

2.1.2 应变硅技术的物理机理

2.1.3 源漏嵌入SiC应变技术

2.1.4 源漏嵌入SiGe应变技术

2.1.5 应力记忆技术

2.1.6 接触刻蚀阻挡层应变技术

2.2 HKMG工艺技术

2.2.1 栅介质层的发展和面临的挑战

2.2.2 衬底量子效应

2.2.3 多晶硅栅耗尽效应

2.2.4 等效栅氧化层厚度

2.2.5 栅直接隧穿漏电流

2.2.6 高介电常数介质层

2.2.7 HKMG工艺技术

2.2.8 金属嵌入多晶硅栅工艺技术

2.2.9 金属替代栅极工艺技术

2.3 SOI工艺技术

2.3.1 SOS技术

2.3.2 SOI技术

2.3.3 PD- SOI

2.3.4 FD- SOI

2.4 FinFET和UTB-SOI工艺技术

2.4.1 FinFET的发展概况

2.4.2 FinFET和UTB- SOI的原理

2.4.3 FinFET工艺技术

参考文献

第3章 工艺集成

3.1 隔离技术

3.1.1 pn结隔离技术

3.1.2 LOCOS(硅局部氧化)隔离技术

3.1.3 STI(浅沟槽)隔离技术

3.1.4 LOD效应

3.2 硬掩膜版工艺技术

3.2.1 硬掩膜版工艺技术简介

3.2.2 硬掩膜版工艺技术的工程应用

3.3 漏致势垒降低效应和沟道离子注入

3.3.1 漏致势垒降低效应

3.3.2 晕环离子注入

3.3.3 浅源漏结深

3.3.4 倒掺杂阱

3.3.5 阱邻近效应

3.3.6 反短沟道效应

3.4 热载流子注入效应和轻掺杂漏(LDD)工艺技术

3.4.1 热载流子注入效应简介

3.4.2 双扩散漏(DDD)和轻掺杂漏(LDD)工艺技术

3.4.3 侧墙(Spacer Sidewall)工艺技术

3.4.4 轻掺杂漏离子注入和侧墙工艺技术的工程应用

3.5 金属硅化物技术

3.5.1 Polycide工艺技术

3.5.2 Salicide工艺技术

3.5.3 SAB工艺技术

3.5.4 SAB和Salicide工艺技术的工程应用

3.6 静电放电离子注入技术

3.6.1 静电放电离子注入技术

3.6.2 静电放电离子注入技术的工程应用

3.7 金属互连技术

3.7.1 接触孔和通孔金属填充

3.7.2 铝金属互连

3.7.3 铜金属互连

3.7.4 阻挡层金属

参考文献

第4章 工艺制程整合

4.1 亚微米CMOS前段工艺制程技术流程

4.1.1 衬底制备

4.1.2 双阱工艺

4.1.3 有源区工艺

4.1.4 LOCOS隔离工艺

4.1.5 阈值电压离子注入工艺

4.1.6 栅氧化层工艺

4.1.7 多晶硅栅工艺

4.1.8 轻掺杂漏(LDD)离子注入工艺

4.1.9 侧墙工艺

4.1.10 源漏离子注入工艺

4.2 亚微米CMOS后段工艺制程技术流程

4.2.1 ILD工艺

4.2.2 接触孔工艺

4.2.3 金属层1工艺

4.2.4 IMD1工艺

4.2.5 通孔1工艺

4.2.6 金属电容(MIM)工艺

4.2.7 金属2工艺

4.2.8 IMD2工艺

4.2.9 通孔2工艺

4.2.10 顶层金属工艺

4.2.11 钝化层工艺

4.3 深亚微米CMOS前段工艺技术流程

4.3.1 衬底制备

4.3.2 有源区工艺

4.3.3 STI隔离工艺

4.3.4 双阱工艺

4.3.5 栅氧化层工艺

4.3.6 多晶硅栅工艺

4.3.7 轻掺杂漏(LDD)离子注入工艺

4.3.8 侧墙工艺

4.3.9 源漏离子注入工艺

4.3.10 HRP工艺

4.3.11 Salicide工艺

4.4 深亚微米CMOS后段工艺技术

4.5 纳米CMOS前段工艺技术流程

4.6 纳米CMOS后段工艺技术流程

4.6.1 ILD工艺

4.6.2 接触孔工艺

4.6.3 IMD1工艺

4.6.4 金属层1工艺

4.6.5 IMD2工艺 1

4.6.6 通孔1和金属层2工艺

4.6.7 IMD3工艺

4.6.8 通孔2和金属层3工艺

4.6.9 IMD4工艺

4.6.10 顶层金属Al工艺

4.6.11 钝化层工艺、

参考文献

第5章 晶圆接受测试(WAT)

5.1 WAT概述

5.1.1 WAT简介

5.1.2 WAT测试类型

5.2 MOS参数的测试条件

5.2.1 阈值电压 V t 的测试条件

5.2.2 饱和电流 I dsat 的测试条件

5.2.3 漏电流 I off 的测试条件

5.2.4 源漏击穿电压 BVD的测试条件

5.2.5 衬底电流 I sub 的测试条件

5.3 栅氧化层参数的测试条件

5.3.1 电容 C gox 的测试条件

5.3.2 电性厚度 T gox 的测试条件

5.3.3 击穿电压 BV gox 的测试条件

5.4 寄生MOS参数测试条件

5.5 pn结参数的测试条件

5.5.1 电容 C jun 的测试条件

5.5.2 击穿电压 BV jun 的测试条件

5.6 方块电阻的测试条件

5.6.1 NW方块电阻的测试条件

5.6.2 PW方块电阻的测试条件

5.6.3 Poly方块电阻的测试条件

5.6.4 AA方块电阻的测试条件

5.6.5 金属方块电阻的测试条件

5.7 接触电阻的测试条件

5.7.1 AA接触电阻的测试条件

5.7.2 Poly接触电阻的测试条件

5.7.3 金属通孔接触电阻的测试条件

5.8 隔离的测试条件

5.8.1 AA隔离的测试条件

5.8.2 Poly隔离的测试条件

5.8.3 金属隔离的测试条件

5.9 电容的测试条件

5.9.1 电容的测试条件

5.9.2 电容击穿电压的测试条件

后记

缩略语

|

| 內容試閱:

|

写作缘由与编写过程

编写本书的想法产生于一个阳光明媚的春天,那是我就职于晶门科技的第四个年头,也就是2014年,如果非要把在中芯国际就职的岁月算进去,应该是我半导体职业生涯的第六 个春秋了。当时为了给公司写一份半导体工艺的培训材料,我重新去读了很多有关半导体工艺方面的专业书籍。在翻阅这些专业书籍的过程中,我了解到虽然目前国内市场上介绍半导体工艺的专业书籍非常多,但是它们大多偏向于理论教学领域,而且很多都是过时的技术,能把理论与实际应用很好地结合的图书非常少,也就是我们通常所说的理论与实际应用脱 节。这就造成很多半导体的同行虽然从事半导体工作多年,但始终对半导体工艺了解很少

因为他们很难从纷繁复杂的半导体工艺书籍中快速提取有用的知识。另外,我也在网上搜集

了很多有关半导体工艺方面的资料,一次偶然的机会我在网上看到几张工艺制程3D图片的PDF文件,感觉这些3D图片画得很有特色,如果对图片添加一些文字注释就可以很好地把 某个工艺制程的过程描述清楚,于是我就萌生了以模仿这些3D图片和外加文字描述的方式 去编写一本半导体工艺方面书籍的想法,这就是编写本书第4章内容的灵感来源。这些经历也是编写本书的开端,万事开头难,既然走出了第一步,后面的事情就是水到渠成的过程了。虽然没那么简单,不过其他章节的内容的确都是以第4章的内容为基础进行扩展的。内容扩展的过程就是一个把我平生所学的工艺知识进行系统归纳整理的过程,也可以理解熟能生巧。编写本书的过程也可谓充满曲折和艰辛,从最初的收集材料到现在的成书阶段,历时四年有余,一千多天,三易其稿,千锤万凿,不断加工润色,所付出的努力都是为了使本 书更加通俗易懂和增加可读性。时至今日也就是我职业生涯的第十个年头,可以说编写这本 书就是十年磨一剑。

下面就和大家聊聊编过程:

第一步是先有第4章的内容。第4章整章的内容都是图文并茂的,采用3D彩图和通俗的文字描述说明一个一个的工艺流程和通过工艺技术形成的IC立体剖面图,通过IC立体剖面图再现通过工艺技术形成的剖面轮廓,生动形象地讲述了工艺制程整合的整个流程。读者可以了解每个工艺步骤的目的和实现过程,做到所有的工艺过程一目了然,摆脱了教科书式 的繁琐理论。这一章内容介绍了亚微米、深亚微米和纳米工艺制程整合的工艺流程,它是整 本书的核心。当然了,开始的时候仅仅只有亚微米工艺制程整合的内容,深亚微米和纳米工艺制程整合的内容是在后来不断完善的过程中加上去的,目的是为了让读者能一目了然地窥探不同工艺技术的相同点和不同点,能快速地了解和掌握它们的特点。

第二步是在第4章内容的基础上延伸出第3章的内容,它也延续了第4章内容的特点,采用图文并茂和3D彩图的描述形式。在编写第4章内容时,我发现没有办法插入非工艺流程的彩图对每个工艺步骤进行详细解释,因为第4章内容主要介绍工艺制程整合的工艺流程,如果强行插入其他内容的图片和介绍则会显得喧宾夺主,内容也会变得不伦不类,所以才出现了第3章的内容。第3章内容是对第4章内容中的工艺模块进行物理机理和产生原因 进行分析解释。例如第3.1节的三种隔离技术(pn结、LOCOS和STI)的原理和随着技术的发展所遇到的瓶颈,以及工艺技术如何一步一步发展克服困难,然后通过实例讲解这些工 艺技术在实际工艺流程中的工程应用,让大家能快速地掌握这些工艺技术。第3章一共7节内容,在这里就不一一介绍了,仅仅列出工艺模块的名称(硬掩膜版、沟道离子注入LDD离子注入、金属硅化物、静电放电离子注入和金属化)。

第三步是在编写完了第3章和第4章内容后,我也希望插入一些很基础的内容,例如对 CVD、PVD、CMP、ETCH、Photo和IMP等进行逐一介绍,但是这部分内容与教材太类似了,在出版社编辑的建议下,最终删掉了这些内容,也就是花费在这些内容上半年多的时

间都付之东流了。仅仅依靠第3章和第4章内容是不能成书的,为了丰富本书的内容,后 来又陆陆续续花了一年左右的时间去编写闩锁效应和ESD电路设计的内容,这部分内容 没有在本书中出现,将会在下一本有关闩锁效应和ESD电路设计的图书中出现,因为后 来成书的时候内容太多了,最后我计划把它们独立成书。另外,第3章和第4章内容写得太具体了,它们不能作为序章,为了对第3章和第4章内容作铺垫,所以写了1章关于集 成电路发展过程的内容作为全书的开端,介绍了集成电路是如何从双极型工艺技术一步一步发展到CMOS工艺技术,首先从双极型工艺技术到PMOS工艺技术,再到NMOS工艺技术。在功耗方面,双极型工艺技术和NMOS工艺技术都遇到了功耗问题,最后引出低功耗的CMOS工艺技术,同时为了适应不断变化的应用需求发展出特色工艺技术(BiC- MOS、BCD和HV- CMOS)。这部分内容后来是1.1节和1.2节的内容,后来又加入了1.3节的内容。

第四步是在编写完了第1章1.1~1.3节的内容后,由于这部分内容是为了引出CMOS工艺技术,它与第3章内容衔接得不是很好,所以就增加了1.4节MOS晶体管按比例缩小的过程中遇到的问题和出现的新技术引出第3章的内容,第3章的内容本质是为了解决这些问题,也可以认为第1.2节的内容是第3章内容的概括总结,它起到衔接作用。

第五步是在编写第1.2节内容的时候,为了搞清楚MOS晶体管在纳米级工艺面临的挑战和出现的新技术,我对应变硅技术、HKMG技术、FD- SOI和FinFET进行了深入学习,从而把这部分内容改编为第2章先进工艺技术的内容。这样第1~4章的内容就富有逻辑和清晰地串联起来了。

第六步是对于这本书如果只有前面4章的内容,那就显得不够完整,而且过于单薄了,所以就编写了第5章关于WAT测试的内容,第5章的内容与第4章的内容紧密相连,把它和第4章的内容串起来,算是晶圆完成工艺制程加工后的出货检测。

第七步是给全书写一个后记,如果把第5章的内容作为末章,会显得过于唐突。后记的内容作为一个总结,探讨了集成电路工艺技术未来的发展和面临的瓶颈。总体来说,本书的编写过程是曲折的,也是呕心沥血的。分享本书的编写过程给大家,是为了给大家一个参照,让大家更好地读懂这本书。本书旨在向从事半导体行业的朋友介绍 集成电路制造工艺与工程应用,目的是为了能提供一本简单易懂并且能与实际工程应用相结合的书。

温德通

|

|