新書推薦:

《

Android游戏开发从入门到精通 第2版 王玉芹

》

售價:NT$

495.0

《

西班牙内战:秩序崩溃与激荡的世界格局:1936-1939

》

售價:NT$

990.0

《

非对称创新:中国企业赶超战略 魏江 刘洋

》

售價:NT$

495.0

《

潜能觉醒

》

售價:NT$

395.0

《

初平:汉末群雄混战(190—195)

》

售價:NT$

245.0

《

建安:官渡大决战(196—200)

》

售價:NT$

245.0

《

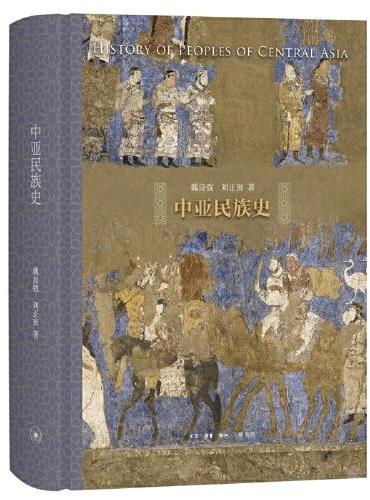

中亚民族史

》

售價:NT$

840.0

![人工智能与智能制造:概念与方法 [美]马苏德·索鲁什 [美]理查德·D.布拉茨](http://103.6.6.66/upload/mall/productImages/24/46/9787111765912.jpg)

《

人工智能与智能制造:概念与方法 [美]马苏德·索鲁什 [美]理查德·D.布拉茨

》

售價:NT$

640.0

|

| 編輯推薦: |

|

PlanAhead工具软件是Xilinx FPGA开发应用的主要软件工具,是用于硬件描述代码完成后进行综合、实现、优化和引脚布局、资源统计等的集成软件工具。掌握PlanAhead工具软件有助于读者进一步提高FPGA的开发能力。

|

| 內容簡介: |

|

PlanAhead工具软件是Xilinx FPGA开发应用的主要软件工具,是用于硬件描述代码完成后进行综合、实现、优化和引脚布局、资源统计等的集成软件工具。本书以V12.2版本的PlanAhead工具软件为基础,详细介绍其功能、特点和使用方法,并通过实例说明PlanAhead工具软件在实现FPGA工程设计管理、RTL设计、网表综合和实现、IO规划、芯片布局、调试验证、资源和性能分析等FPGA设计过程的应用,使读者能够全面了解和掌握PlanAhead工具软件的使用,并能够据此设计出资源使用合理、综合频率较高的实用化设计方案。

|

| 關於作者: |

|

刘东华,男,博士,副教授,中国科学院计算技术研究所博士后,现工作于国防科技大学电子科学与工程学院。主要从事通信技术方面的研究工作。

|

| 目錄:

|

第1章 概述

1.1 PlanAhead简介

1.1.1 PlanAhead工具软件的功能特点

1.1.2 PlanAhead工具软件的启动

1.1.3 PlanAhead设计流程

1.1.4 使用模式

1.2 ISE与PlanAhead的交互

1.2.1 工具软件集成

1.2.2 在ISE中启动PlanAhead工具软件

1.3 PlanAhead术语

第2章 PlanAhead集成开发环境

2.1 主菜单

2.1.1 File菜单

2.1.2 Edit菜单

2.1.3 View菜单

2.1.4 Flow菜单

2.1.5 Tool菜单

2.1.6 Windows菜单

2.1.7 Select菜单

2.1.8 Layout菜单

2.1.9 Help菜单

2.2 主工具条

2.3 设计流导航工具

2.3.1 基于RTL源的设计流导航

2.3.2 基于综合网表工程的设计流导航

2.3.3 从设计流导航启动命令

2.3.4 设计流导航工具的使用

2.4 主视图区域

2.5 状态栏

2.6 消息视图和Tcl控制台

2.6.1 消息视图

2.6.2 Tcl控制台

2.7 信息栏

第3章 常用视图及操作

3.1 视图操作

3.1.1 打开视图

3.1.2 视图导航

3.1.3 移动视图

3.2 图形化视图

3.3 树形列表视图

3.4 视图对象操作

3.5 常用视图

3.5.1 源视图

3.5.2 芯片视图

3.5.3 封装视图

3.5.4 原理图视图

3.5.5 属性视图

3.5.6 网表视图

3.5.7 层次视图

3.5.8 IO端口视图

3.5.9 封装引脚视图

3.5.10 设计运行视图

3.6 文本编辑器

第4章 PlanAhead工程设计

4.1 创建新工程

4.1.1 新建工程向导

4.1.2 基于RTL源文件创建工程

4.1.3 基于综合网表创建工程

4.1.4 创建IO引脚规划工程

4.1.5 导入ISE布局布线结果

4.2 工程管理

4.2.1 RTL源文件管理

4.2.2 约束管理

4.2.3 IP核管理

4.3 工程概要信息

4.4 配置工程设置

4.5 输入和输出文件

4.5.1 输入文件

4.5.2 输出文件

第5章 RTL设计

5.1 设计源文件管理

5.2 编辑RTL源文件

5.3 细化和分析RTL设计

5.3.1 细化RTL设计

5.3.2 资源估计

5.4 功耗估计

5.5 RTL设计规则检查(DRC)

第6章 综合设计

6.1 设计综合

6.1.1 综合的方法

6.1.2 运行综合

6.1.3 监视综合运行

6.1.4 选择综合后的操作

6.1.5 分析综合结果

6.1.6 启动多个运行

6.1.7 管理多个运行

6.2 网表分析

6.2.1 网表设计环境

6.2.2 查看和报告资源统计

6.2.3 逻辑分析

6.2.4 插入ChipScope调试IP核

6.3 约束定义

6.3.1 定义时序约束

6.3.2 运行时序分析

6.3.3 延时直方图

6.4 网表和约束DRC

第7章 IO引脚规划

7.1 IO规划概述

7.2 芯片资源查看

7.3 定义兼容芯片和设置芯片配置模式

7.4 定义和配置IO端口

7.5 指定IO端口

7.6 检查IO和时钟逻辑指定

7.7 其他IO操作

7.8 引脚规划实例

第8章 实现设计

8.1 实现设计

8.1.1 运行设计

8.1.2 监视运行状态

8.1.3 判断工程状态

8.1.4 选择实现后的操作

8.1.5 分析运行结果

8.1.6 启动多个运行

8.1.7 管理多个运行

8.2 分析实现结果

8.2.1 打开实现的设计

8.2.2 导入ISE结果

8.2.3 分析布局和时序结果

8.2.4 分析逻辑连接

8.2.5 高亮显示和标记对象

8.2.6 锁定布局

8.2.7 显示设计度量

8.2.8 启动XPower分析器

8.2.9 交叉探测时序路径

第9章 布局设计

9.1 Pblock

9.2 Pblock的配置

9.3 布局LOC约束的使用

9.4 与ISE的接口

第10章 编程和调试设计

10.1 生成比特流

10.1.1 BitGen

10.1.2 在PlanAhead中使用BitGen

10.2 用ChipScope调试设计

10.3 启动ChipScope Pro分析仪

10.4 启动iMPACT

第11章 分层设计技术

11.1 PlanAhead和ISE的功能理解

11.2 使用PlanAhead进行设计保留

11.3 分层设计实例

第12章 Tcl脚本和命令

12.1 PlanAhead工具软件的Tcl功能

12.2 启动PlanAhead软件

12.3 常用的Tcl语法

12.4 第一类Tcl对象和关系

12.5 出错、警告和信息消息

12.6 Tcl命令

参考文献

|

|

![人工智能与智能制造:概念与方法 [美]马苏德·索鲁什 [美]理查德·D.布拉茨](http://103.6.6.66/upload/mall/productImages/24/46/9787111765912.jpg)