新書推薦:

《

直观的经营:哲学视野下的动态管理

》

售價:NT$

407.0

《

长高食谱 让孩子长高个的饮食方案 0-15周岁儿童调理脾胃食谱书籍宝宝辅食书 让孩子爱吃饭 6-9-12岁儿童营养健康食谱书大全 助力孩子身体棒胃口好长得高

》

售價:NT$

214.0

《

身体自愈力:解决内在病因的身体智慧指南

》

售價:NT$

449.0

《

非言语沟通经典入门:影响人际交往的重要力量(第7版)

》

售價:NT$

560.0

《

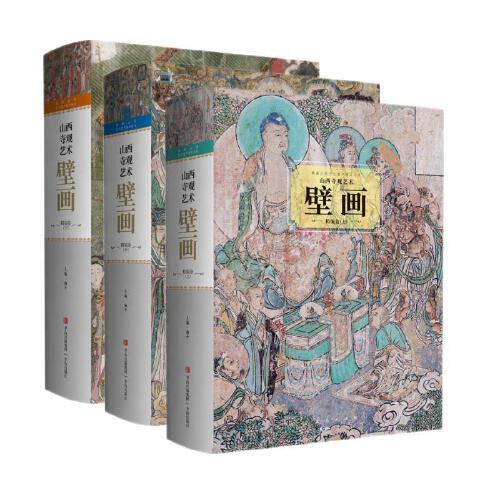

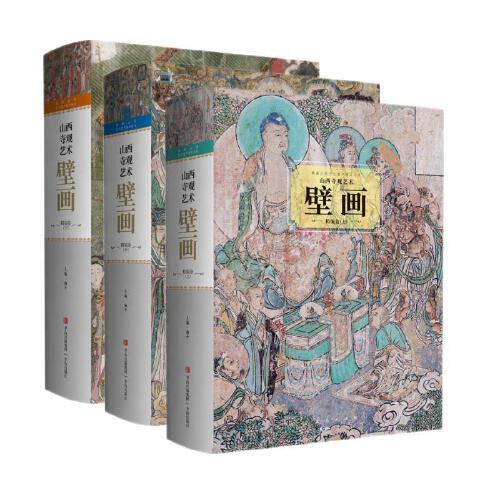

山西寺观艺术壁画精编卷

》

售價:NT$

7650.0

《

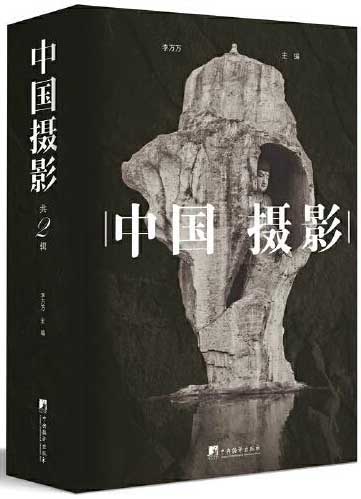

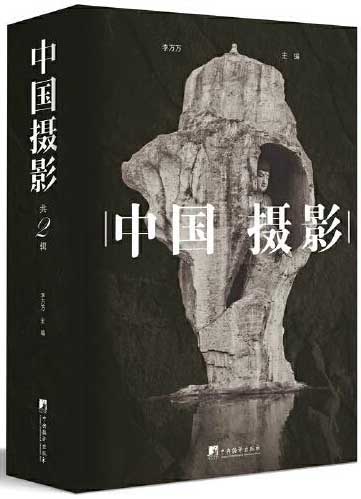

中国摄影 中式摄影的独特魅力

》

售價:NT$

4998.0

《

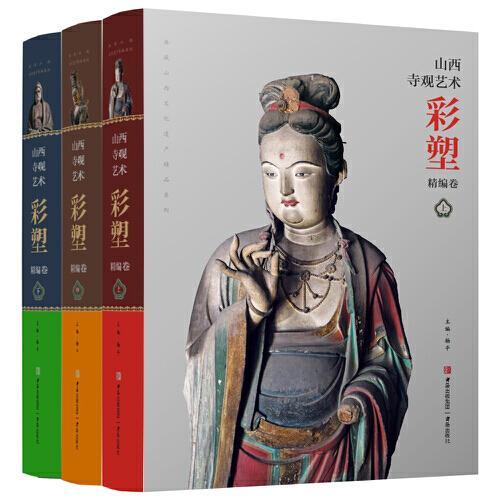

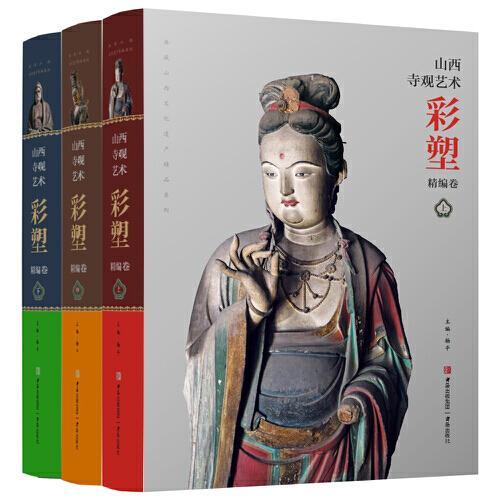

山西寺观艺术彩塑精编卷

》

售價:NT$

7650.0

《

积极心理学

》

售價:NT$

254.0

|

| 編輯推薦: |

1.注重Verilog HDL语法基础和设计方法

2.结合当前技术发展,加入对嵌入式系统设计、片上系统设计、设计校验等内容的介绍

3.各章节相对独立,不同专业可有所取舍

|

| 內容簡介: |

书采用Verilog

HDL语言,较为系统地介绍了EDA设计技术的语法基础、基本原理和设计方法。全书共12章,分为逻辑器件和语言基础、EDA设计方法、EDA设计工具、Nios

Ⅱ处理器及嵌入式系统设计四大部分,主要内容包括Verilog

HDL语言基础,可编程逻辑器件结构,各级抽象的建模设计方法,功能校验和时序校验设计方法,Quartus Ⅱ、ModelSim和Nios

Ⅱ SBT for Eclipse设计工具,基于Nios

Ⅱ的嵌入式系统设计流,配置BSP工程和应用工程,硬件抽象层及其API服务等。各章节配有实例和习题,所有实例均通过编译和验证。

本书可作为电子信息工程、通信工程、电气工程及其自动化等相关专业本科学生的教材,也可作为研究生或工程技术人员的参考书。

|

| 目錄:

|

第1章 绪论

1.1 EDA技术

1.1.1 EDA设计的技术优势

1.1.2 EDA设计流

1.2 可编程逻辑器件及其开发环境

1.3 知识产权核及片上系统

习题

第2章 可编程逻辑器件

2.1 可编程逻辑阵列PLA

2.2 可编程阵列逻辑器件PLD

2.3 通用逻辑阵列器件GAL

2.4 CPLD结构

2.4.1 逻辑阵列块

2.4.2 逻辑单元

2.4.3 用户Flash存储块

2.4.4 输入输出口

2.5 FPGA结构

2.5.1 嵌入式乘法器

2.5.2 输入输出口

2.5.3 时钟网络和锁相环逻辑块

2.5.4 高速差分接口

2.5.5 存储器块

2.6 配置与编程

2.6.1 在系统编程接口

2.6.2 设计安全

习题

第3章 Verilog HDL语言

3.1 Verilog HDL的历史及特点

3.2 标识符与关键字

3.3 注释

3.4 格式

3.5 数据类型

3.5.1 值集合

3.5.2 矢量与标量

3.5.3 数组

3.5.4 参数

3.5.5 字符串

3.5.6 网络类型

3.5.7 变量类型

3.6 赋值

3.6.1 连续赋值

3.6.2 过程赋值

3.7 表达式

3.7.1 操作数

3.7.2 操作符

3.8 强度

3.8.1 电荷强度

3.8.2 驱动强度

3.9 编译指令

3.9.1 宏定义

3.9.2 条件定义

3.9.3 默认类型

3.9.4 文件包含

3.9.5 复位编译器指令

3.9.6 时间单位

3.10 系统任务和系统函数

3.10.1 信息显示

3.10.2 跟踪显示与触发显示

3.10.3 仿真时间函数

3.10.4 停止仿真任务

3.10.5 仿真随机函数

习题

第4章 层次结构

4.1 系统及结构要素

4.2 设计方法

4.3 模块及模块抽象

4.3.1 模块

4.3.2 模块抽象

4.4 例化

4.4.1 模块例化

4.4.2 原语例化

4.4.3 生成例化与等价验证

习题

第5章 行为建模

5.1 过程语句

5.1.1 initial语句

5.1.2 always语句

5.1.3 阻塞式过程赋值

5.1.4 非阻塞式过程赋值

5.2 延时控制

5.3 条件语句

5.4 条件运算符

5.5 循环语句

5.5.1 repeat语句建模

5.5.2 for语句建模

5.5.3 while语句建模

5.5.4 forever语句建模

5.5.5 异常情况下退出循环

5.6 多路分支语句

5.7 任务和函数

5.7.1 任务

5.7.2 函数

5.7.3 函数和任务的比较

5.7.4 共享任务和函数

5.8 行为建模实例

5.8.1 交通灯演示模型

5.8.2 伺服电机调速控制器

习题

第6章 并行建模

6.1 事件控制

6.1.1 边沿触发事件控制

6.1.2 电平敏感事件控制

6.2 等待控制

6.3 顺序控制

6.4 并行控制

6.5 并行建模实例

习题

第7章 逻辑设计

7.1 组合逻辑设计

7.1.1 多路开关

7.1.2 译码器

7.1.3 编码器

7.1.4 比较器

7.1.5 加法器和减法器

7.1.6 乘法器

7.1.7 初等函数与通用查找表

7.2 时序逻辑设计

7.2.1 锁存器和触发器

7.2.2 有限状态机

7.2.3 计数器

习题

第8章 用户定义原语建模

8.1 定义用户定义原语

8.1.1 用户定义原语的基本形式

8.1.2 用户定义原语的表符号

8.1.3 组合逻辑UDP

8.1.4 时序逻辑UDP

8.1.5 时序UDP的初始化

8.2 用户定义原语建模

习题

第9章 设计校验

9.1 设计校验概述

9.1.1 校验标准

9.1.2 等价验证

9.1.3 模块检查

9.1.4 校验重用

9.1.5 校验方法

9.2 功能校验

9.2.1 测试平台

9.2.2 代码封装

9.2.3 数据抽象

9.2.4 竞争

9.3 时序校验

9.3.1 延时类型

9.3.2 路径延时

9.3.3 时序检查

9.3.4 标准延时格式文件与反向标注

习题

第10章 Quartus Ⅱ开发环境

10.1 工程设计流程

10.1.1 Quartus Ⅱ设计流程

10.1.2 Quartus Ⅱ及EDA工具设计流程

10.2 设计输入

10.2.1 创建工程

10.2.2 块编辑器

10.2.3 文本编辑器

10.2.4 状态机编辑器

10.2.5 参数化模块库

10.2.6 约束输入

10.3 综合

10.4 布局与布线

10.4.1 分析适配结果

10.4.2 优化适配

10.5 时序分析

10.5.1 TimeQuest时序分析器

10.5.2 标准时序分析器

10.5.3 时序分析流程

10.6 时序逼近

10.6.1 平面布局图或器件布局图

10.6.2 时序优化向导

10.6.3 使用网表优化实现时序逼近

10.6.4 时序逼近设计方法

10.7 功耗分析

10.7.1 功耗分析器工具

10.7.2 早期功耗估算

10.8 编程与配置

10.8.1 编程文件与编程设置

10.8.2 编程模式与编程电缆联机

10.8.3 编程操作

10.9 形式验证

10.9.1 形式验证工具

10.9.2 形式验证工具设置

10.10 系统集成工具

10.11 系统调试工具

习题

第11章 ModelSim仿真工具

11.1 ModelSim SE简介

11.1.1 ModelSim SE的主窗口及仿真流程

11.1.2 创建工程和工作库

11.1.3 编译仿真文件

11.1.4 加载顶层设计模块

11.1.5 执行仿真

11.1.6 调试

11.2 库的创建和运用

11.3 波形分析

11.3.1 仿真波形窗口介绍

11.3.2 缩放波形

11.3.3 时标

11.3.4 输出波形文件

11.4 时序仿真

11.5 例化存储器

11.6 用Profiler进行性能分析

11.7 代码覆盖率

11.8 值变转储文件

11.8.1 转储系统任务

11.8.2 四态转储文件

11.8.3 扩展转储文件

11.8.4 操作VCD文件

习题

第12章 基于Nios Ⅱ的嵌入式系统设计

12.1 Nios Ⅱ处理器

12.1.1 算术逻辑单元

12.1.2 寄存器

12.1.3 异常处理

12.1.4 存储器和输入输出口

12.1.5 运行模式及存储器管理

12.1.6 地址空间和存储器分区

12.1.7 调试和复位信号

12.1.8 JTAG调试模块

12.1.9 指令集

12.1.10 处理器的内核类型选择

12.1.11 例化Nios Ⅱ处理器

12.2 Avalon接口

12.3 嵌入式系统设计流

12.4 软件设计

12.4.1 配置BSP工程和应用工程

12.4.2 硬件抽象层API设计

12.4.3 优化设计

12.4.4 系统启动配置

习题

参考文献

索引

|

|