新書推薦:

《

自由,不是放纵

》

售價:NT$

250.0

《

甲骨文丛书·消逝的光明:欧洲国际史,1919—1933年(套装全2册)

》

售價:NT$

1265.0

《

剑桥日本戏剧史(剑桥世界戏剧史译丛)

》

售價:NT$

918.0

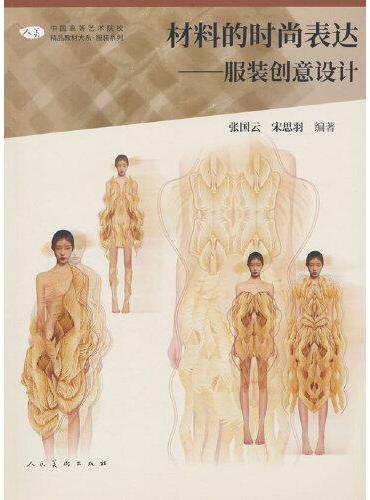

《

中国高等艺术院校精品教材大系:材料的时尚表达??服装创意设计

》

售價:NT$

347.0

《

美丽与哀愁:第一次世界大战个人史

》

售價:NT$

653.0

《

国家豁免法的域外借鉴与实践建议

》

售價:NT$

857.0

《

大单元教学设计20讲

》

售價:NT$

347.0

《

儿童自我关怀练习册:做自己最好的朋友

》

售價:NT$

316.0

|

| 內容簡介: |

|

本书根据电子类课程课堂教学和实验的要求,以提高学生的动手实践能力和工程设计能力为目的,对EDA技术和FPGA设计的相关知识进行系统和完整的介绍。本书内容新颖,技术先进,由浅入深,既有关于EDA技术、FPGA器件和Verilog硬件描述语言的系统介绍,又有丰富的设计实例。本书配套多媒体电子课件、实验与设计和程序代码。

|

| 關於作者: |

|

徐志军,中国高等教育学会仪器科学及测控技术专业委员会副主任委员、华东地区高校电子线路教学研究会理事、中国电子学会高级会员,普通高等教育“十一五”国家级规划教材《EDA技术与VHDL设计》畅销书作者,该书是本书的姊妹篇。

|

| 目錄:

|

第1章 EDA技术概述

1.1 EDA技术及其发展历程

1.2 EDA技术的特征和优势

1.2.1 EDA技术的特征

1.2.2 EDA技术的优势

1.3 EDA设计的目标和流程

1.3.1 EDA设计的目标

1.3.2 EDA设计的流程

1.3.3 数字集成电路的设计

1.3.4 模拟集成电路的设计

1.4 EDA技术与ASIC设计

1.4.1 ASIC的特点与分类

1.4.2 ASIC的设计方法

1.4.3 SoC设计

1.5 硬件描述语言

1.5.1 VHDL

1.5.2 Verilog HDL

1.5.3 ABEL-HDL

1.5.4 Verilog HDL和VHDL的比较

1.6 EDA设计工具

1.6.1 EDA设计工具分类

1.6.2 EDA公司及其工具介绍

1.7 EDA技术的发展趋势

习题

第2章 可编程逻辑器件基础

2.1 概述

2.1.1 可编程逻辑器件的发展历程

2.1.2 可编程逻辑器件的分类

2.1.3 可编程逻辑器件的优势

2.1.4 可编程逻辑器件的发展趋势

2.2 PLD器件的基本结构

2.2.1 基本结构

2.2.2 电路符号

2.2.3 PROM

2.2.4 PLA

2.2.5 PAL

2.2.6 GAL

2.3 CPLDFPGA器件概述

2.3.1 Lattice的CPLDFPGA

2.3.2 Xilinx的CPLDFPGA

2.3.3 Altera的CPLDFPGA

2.3.4 CPLD和FPGA的异同

2.4 可编程逻辑器件的基本资源

2.4.1 功能单元

2.4.2 IO引脚

2.4.3 布线资源

2.4.4 片内RAM

2.5 可编程逻辑器件的编程元件

2.5.1 熔丝型开关

2.5.2 反熔丝型开关

2.5.3 浮栅编程元件

2.5.4 基于SRAM的编程元件

2.6 可编程逻辑器件的设计与开发

2.6.1 CPLDFPGA设计流程

2.6.2 CPLDFPGA开发工具

2.6.3 CPLDFPGA的应用选择

2.7 可编程逻辑器件的测试技术

2.7.1 边界扫描测试原理

2.7.2 IEEE1149.1 标准

2.7.3 边界扫描策略及相关工具

习题

第3章 典型FPGACPLD的结构与配置

3.1 Stratix高端FPGA系列

3.1.1 Stratix器件

3.1.2 StratixⅡ器件

3.2 Cyclone低成本FPGA系列

3.2.1 Cyclone器件

3.2.2 CycloneⅡ器件

3.3 典型CPLD器件

3.3.1 MAXⅡ器件

3.3.2 MAX7000器件

3.4 FPGACPLD的配置

3.4.1 CPLD器件的配置

3.4.2 FPGA器件的配置

习题

第4章 QuartusⅡ集成开发工具

4.1 QuartusⅡ原理图设计

4.1.1 半加器原理图设计输入

4.1.2 编译与仿真

4.1.3 1位全加器编译与仿真

4.2 QuartusⅡ的优化设置

4.2.1 分析与综合设置

4.2.2 优化布局布线

4.2.3 设计可靠性检查

4.3 QuartusⅡ的时序分析

4.3.1 时序设置与分析

4.3.2 时序逼近

4.4 基于宏功能模块的设计

4.4.1 Megafunctions库

4.4.2 Maxplus2库

4.4.3 Primitives库

习题

实验与设计

第5章 VerilogHDL语法与要素

5.1 VerilogHDL简介

5.2 VerilogHDL模块的结构

5.3 VerilogHDL语言要素

5.4 常量

5.4.1 整数

5.4.2 实数

5.4.3 字符串

5.5 数据类型

5.5.1 net型

5.5.2 variable型

5.6 参数

5.7 向量

5.8 运算符

习题

实验与设计

第6章 VerilogHDL行为语句

第7章 VerilogHDL设计的层次与风格

第8章 VerilogHDL设计进阶

第9章 VerilogHDL仿真与测试

第10章 VerilogHDL数字设计实例

第11章 VerilogHDL数字通信常用模块设计实例

实验与设计

附录A Verilog HDL(IEEEStd1364-1995)关键字

附录B Verilog HDL(IEEEStd1364-2001)关键字

参考文献

|

|