新書推薦:

《

云中记

》

售價:NT$

347.0

《

中国古代妇女生活(中国古代生活丛书)

》

售價:NT$

214.0

《

你的认知正在阻碍你

》

售價:NT$

296.0

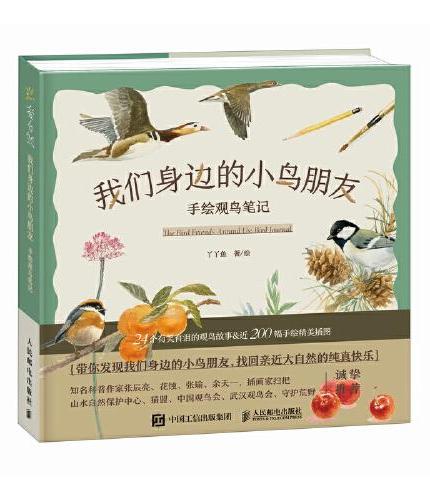

《

我们身边的小鸟朋友:手绘观鸟笔记

》

售價:NT$

356.0

《

拯救免疫失衡

》

售價:NT$

254.0

《

收尸人

》

售價:NT$

332.0

《

大模型应用开发:RAG入门与实战

》

售價:NT$

407.0

《

不挨饿快速瘦的减脂餐

》

售價:NT$

305.0

|

| 內容簡介: |

作者从2009年1月起,在《电子世界》杂志上连载了《手把手教你学CPLD/FPGA设计》讲座。本书以此为蓝本,另外增加了大量的篇幅与实验例子进行充实。此外,为了帮助读者掌握单片机与CPLD/FPGA的联合设计,还介绍了51单片机的基本知识及单片机c语言编程的基础知识,并通过实例设计进行详解。本书以实践(实验)为主线,以生动短小的实例为灵魂,穿插介绍了Verilog HDL语言的语法及Altera公司的EPM7128S(或Atmel公司的ATFl508A5)设计开发编程。本书理论与实践紧密结合,由浅入深、循序渐进地引导读者进行学习、实验,这样读者学得进、记得牢,不会产生畏难情绪,无形之中就掌握了CPLD/FPGA的联合设计。

本书贯彻《手把手教你学系列丛书》的教学方式。书中附有光盘,含本书所有的程序设计文件。本书可用作大学本科或专科、中高等职业技术学校、电视大学等的教学用书,也可作为CPLD/FPGA爱好者的自学用书。

|

| 目錄:

|

第1章 可编程逻辑器件概述

1.1 可编程逻辑器件简介

1.1.1 可编程逻辑器件的基本结构

1.1.2 可编程逻辑器件的分类及特点

1.1.3 可编程逻辑器件的逻辑表示方法

1.2 CPLD/FPGA的结构与特性

1.2.1 基于乘积项的CPLD原理与结构

1.2.2 基于乘积项的CPLD逻辑实现方式

1.2.3 基于查找表的FPGA原理与结构

1.2.4 基于查找表的FPGA逻辑实现方式

1.2.5 CPLD与FPGA器件的差别

1.3 Altera公司的MAX7000系列2PLD特性介绍

1.3.1 逻辑阵列块LAB

1.3.2 宏单元

1.3.3 扩展乘积项

1.3.4 可编程连线阵列

1.3.5 I/O控制块

1.3.6 其他特性

第2章 可编程逻辑器件的设计流程及学习开发器材

2.1 可编程逻辑器件的设计流程

2.1.1 设计输入

2.1.2 综合

2.1.3 CPLD/FPGA器件适配

2.1.4 仿真

2.1.5 编程下载

2.2 CPLD/FPGA与单片机联合设计的学习器材介绍

2.2.1 Altera公司的集成开发软件MAX+plusII及QuartusII

2.2.2 KeiIC51Windows集成开发环境

2.2.3 MCU&CPLDDEMO综合试验板

2.2.4 ByteBlasterMV并口下载器

2.2.5 单片机USB程序下载器

2.2.6 9V高稳定专用稳压电源

第3章 开发软件的安装

3.1 KeilC51集成开发软件安装

3.2 MAX+plusⅡ集成开发软件安装

3.3 QuartusⅡ集成开发软件安装

3.4 USBasp下载器的安装与使用

3.4.1 USBasp下载器的安装

3.4.2 USBasp下载器的使用

3.5 Atmel并口下载软件atmelisp的安装

3.6 POF to JED转换软件Pof2jed的安装

第4章 第一个CPLD/FPGA入门实验程序

4.1 使用Max+plusⅡ集成开发软件进行入门实验

4.1.1 建立项目

4.1.2 设计输入原理图或硬件描述语言

4.1.3 选择器件并锁定引脚

4.1.4 编译器件

4.1.5 仿真

4.1.6 编程下载

4.1.7 应用

4.2 使用QuartusⅡ集成开发软件进行入门实验

4.2.1 建立项目

4.2.2 设计输入原理图或硬件描述语言

4.2.3 设计编译

4.2.4 仿真

4.2.5 引脚分配

4.2.6 编程下载

4.2.7 立用

第5章 VerilogHDL硬件描述语言

5.1 VerilogHDL模块的基本结构

5.1.1 模块声明

5.1.2 端口定义

5.1.3 信号类型说明

5.1.4 逻辑功能描述

5.1.5 实验程序1——缓冲器

5.1.6 实验程序2——反相器非门

5.2 VerilogHDL语法要素

5.2.1 标识符与关键字

5.2.2 常量、变量及数据类型

5.2.3 实验程序3——与门

5.2.4 实验程序4——与非门

5.2.5 实验程序5——LED的闪烁

5.2.6 运算符

5.2.7 运算符的优先级

5.2.8 实验程序6——或门

5.2.9 实验程序7——或非门

5.2.10 实验程序8——异或门

5.2.11 实验程序9——异或非门

5.2.12 实验程序10——三态门

5.3 VerilogHDL的行为语句

5.3.1 赋值语句

5.3.2 过程语句

5.3.3 块语句

5.3.4 条件语句

5.3.5 循环语句

5.3.6 编译预处理

5.3.7 任务和函数

5.4 VerilogHDL数字逻辑单元结构的设计

5.4.1 结构描述方式

5.4.2 实验程序——门级结构描述设计的基本门电路

5.4.3 数据流描述方式

5.4.4 行为描述方式

第6章 组合逻辑电路的设计实验

第7章 触发器的设计实验

第8章 时序逻辑电路的设计实验

第9章 CPLDFPGA的设计应用

第10章 51单片机的基本知识

第11章 单片机C语言基础知识

第12章 CPLDFPGA与单片机的接口及数据传输

第13章 CPLDFPGA与单片机的联合设计实例——液晶显示频率计

参考文献

|

| 內容試閱:

|

第1章 可编程逻辑器件概述

多年来,人们设计数字电路系统都是使用标准的数字集成电路芯片,如74/54系列TTL、4000/4500系列CMOS等,根据设计的功能从这些标准的芯片中进行选择,然后搭建成一个完整的数字电路应用系统。使用这种方法设计出来的系统,不仅芯片数量多、印板面积大,而且可靠性差,毫无设计的灵活性可言。

可编程逻辑器件PLDProgrammable Logic Device出现后,改变了人们的传统设计方法,可以直接使用PLD芯片进行数字电路系统的设计。例如,可以直接设计芯片内部的数字逻辑并定义输入/输出引脚等,从原来的印板级设计上升到芯片级设计。由于PLD设计时引脚定义非常灵活,不仅降低了电路原理和印板设计的难度,提高了设计效率,而且大大减少了芯片的数量和种类,缩小了印板面积,降低了功耗,并极大地提高了系统工作的可靠性。

……

|

|