新書推薦:

《

匹诺曹:非存在的存在(阿甘本另类解读《木偶奇遇记》 流浪木偶匹诺曹的哲学启示)

》

售價:NT$

337

《

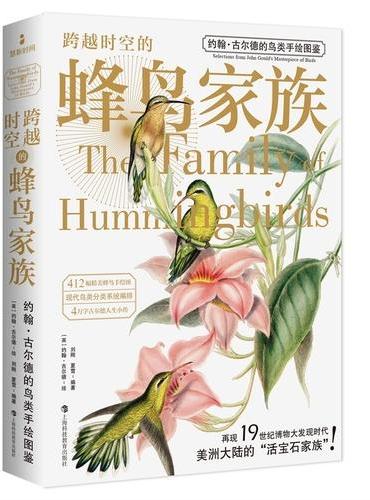

跨越时空的蜂鸟家族(约翰·古尔德的鸟类手绘图鉴)

》

售價:NT$

857

《

成功的法则:掌控人生的关键能力

》

售價:NT$

301

《

黄宗羲传

》

售價:NT$

347

《

教育研究量表手册 21世纪教育科学系列教材

》

售價:NT$

454

《

真事隐:康熙废储与正史虚构

》

售價:NT$

398

《

工艺之美(席曼婷)

》

售價:NT$

454

《

揭秘煤气灯效应:心理操控的哲学透视

》

售價:NT$

281

|

| 編輯推薦: |

本书覆盖了在深亚微米CMOS工艺中进行下一代微处理器设计的各个方面,书中的各章都由世界上著名的技术专家、设计师和研究人员编写而成。虽然微处理器系统设计的各个层面都有涉及,但重点是电路设计。本书中的例子都是从世界著名公司处理器中选取的。

本书中每章涉及的内容是独立的,因此各章之间的阅读次序是无关紧要的。各章内容包括:泄漏功耗降低技术、低电压技术、SOI工艺与电路、钟控存储单元、时钟分配、互连驱动技术、IO和ESD电路设计、供电网络的设计与分析等。

|

| 內容簡介: |

本书论述了高性能微处理器电路设计的几乎所有方面,包括工艺技术对微处理器体系结构的影响、考虑工艺参数变动情况下的器件和连线模型、高速算术逻辑单元的设计、低电压设计技术、泄漏功耗降低技术、时钟分配、供电分配、高速信号传输、寄存器文件和缓存设计、芯片测试等等。

本书可供从事电子电路设计的相关技术人员参考,也可作为微电子专业高年级本科生和研究生的教材。

|

| 關於作者: |

钱德拉卡山

是麻省理工学院电气工程与计算机科学系的副教授。Chandrakasan博士获得了很多奖,并在多个IEEE和ACM会议上担任技术程序委员。他的研究领域包括DSP的高效能实现、无线微传感器网络和VLSI的CAD工具。

|

| 目錄:

|

译者序

原书序

第1章 物理工艺对体系结构的影响1

1.1 引言1

1.2 CMOS工艺下处理器体系结构的实现3

1.3 高性能微处理器周期时间的选择12

1.4 PA8000、21164和21264处理器的比较13

1.5 互连电阻的趋势14

1.6 功耗趋势15

1.7 高级封装19

1.8 小结20

参考文献21

第2章 CMOS器件尺寸缩小和亚0.25μm系统中的问题22

2.1 MOSFET缩小理论22

2.2 0.25μm以下工艺中CMOS的缩小问题26

2.3 互连RC延迟33

2.4 低温CMOS35

参考文献38

第3章 泄漏功耗降低技术39

3.1 引言39

3.2 晶体管泄漏电流组成成分40

3.3 电路亚阈值泄漏电流44

3.4 泄漏控制技术47

参考文献53

第4章 低电压技术55

4.1 低电压低阈值电路设计55

4.2 电源关断方案58

4.3 衬底偏置控制的Vth59

4.4 处理器设计举例67

4.5 小结70

参考文献71

第5章 SOI工艺与电路73

5.1 引言73

5.2 PDSOI与FD SOI的器件设计考虑73

5.3 器件结果75

5.4 PD-SOI CMOS 数字电路79

5.5 低功耗SOI87

5.6 小结88

参考文献89

第6章 器件和互连线的工艺参数变动模型90

6.1 引言——变动来源90

6.2 概述——统计描述91

6.3 工艺参数变动综述93

6.4 刻画和处理参数变动的方法96

6.5 在互连影响分析问题上的应用100

6.6 小结105

参考文献105

第7章 高速VLSI算术单元:加法器和乘法器107

7.1 高速加法:算法和VLSI实现107

7.2 乘法120

7.3 小结128

参考文献128

第8章 钟控存储单元131

8.1 时钟策略概述131

8.2 时钟信号的非理想特性132

8.3 基本锁存器对134

8.4 基本触发器135

8.5 鲁棒性设计准则1137

8.6 时序逻辑的时序特性139

8.7 锁存器对和触发器的比较144

8.8 高性能钟控存储单元145

8.9 鲁棒性设计准则2151

8.10 钟控存储单元的性能指标153

8.11 动态电路的锁存单元 154

8.12 建议和小结156

参考文献157

第9章 时钟分配158

9.1 引言158

9.2 目标162

9.3 实现165

9.4 时钟驱动器版图170

9.5 变动173

9.6 小结176

参考文献176

第10章 寄存器文件和缓冲存储器179

10.1 基本结构179

10.2 基本SRAM单元的设计和操作184

10.3 地址路径的设计192

10.4 读路径设计194

10.5 写路径设计198

10.6 冗余199

10.7 可靠性问题200

参考文献201

第11章 分析片上互连效应202

11.1 引言202

11.2 简化的互连线分析205

11.3 模型降阶209

11.4 驱动器模型216

11.5 小结221

参考文献221

第12章 互连驱动技术223

12.1 工艺尺寸缩小趋势223

12.2 与电容效应有关的问题和解决办法230

12.3 与电感效应有关的问题和解决办法234

12.4 与电阻效应有关的问题和解决办法241

12.5 长距离布线的问题和解决办法241

12.6 小结245

参考文献246

第13章 IO和ESD电路设计247

13.1 引言247

13.2 供电的考虑因素247

13.3 片外驱动电路的边沿速率控制249

13.4 混合电压IO251

13.5 阻抗匹配254

13.6 预补偿驱动器254

13.7 输入接收器255

13.8 ESD威胁256

13.9 ESD模型256

13.10 ESD保护网络的电路拓扑258

13.11 ESD保护设计元件和方法259

13.12 电源钳位263

13.13 CDM的考虑因素264

参考文献265

第14章 高速芯片间的信号传输267

14.1 传输线268

14.2 信号链路的性能指标272

14.3 发送器275

14.4 接收器281

14.5 时钟信号生成284

14.6 未来趋势289

14.7 小结293

参考文献294

第15章 计算机辅助设计工具概述297

15.1 引言297

15.2 微体系结构设计和电路可行性研究工具298

15.3 RTL模型设计工具299

15.4 RTL数据通路存储器设计工具301

15.5 控制逻辑设计工具303

15.6 芯片装配和总体线网布线304

15.7 芯片级版图、电路以及时序验证304

15.8 测试模式生成306

15.9 结论307

参考文献307

第16章 时序验证308

16.1 引言308

16.2 时序验证的目标和分析308

16.3 高速设计和时序验证中的关键因素312

16.4 非存储器定制模块的时序验证317

16.5 存储器模块的时序验证319

16.6 设计流程和全芯片时序验证321

16.7 未来的挑战324

参考文献325

第17章 供电网络的设计与分析326

17.1 引言326

17.2 供电网络设计327

17.3 供电网格分析337

17.4 供电网格建模340

17.5 小结346

参考文献346

第18章 高性能处理器测试349

18.1 引言349

18.2 测试的基本概念349

18.3 可测试性设计355

18.4 小结369

参考文献369

|

|